"분위기 반전 노린다" HBM3E 12단·HBM4에 총력 기울이는 삼성전자

입력

수정

삼성전자, 2분기 중 HBM3E 12단 양산·납품 착수

'엔비디아-TSMC-SK하이닉스' 3사 협력 뒤흔들 수 있을까

HBM4 로직 다이 제작에는 4㎚ 파운드리 공정 적용 예정

삼성전자가 고대역폭메모리(HBM) 시장 패권 확보를 위해 속도를 내고 있다. 경쟁사 SK하이닉스에 주도권을 빼앗긴 HBM3E(5세대 HBM) 8단 시장을 뒤로하고 HBM3E 12단, HBM4(6세대 HBM) 등 첨단 제품에 무게를 실으며 초기 시장 선점에 힘을 쏟는 양상이다.

HBM3E 12단에 승부수

16일 관련 업계에 따르면 삼성전자는 지난 2분기 HBM3E 12단 제품의 양산에 돌입했으며, 현재 일부 고객사들에 이를 납품하고 있다. HBM3E 12단은 실리콘 관통 전극(TSV) 기술을 활용해 D램 메모리 칩을 12단까지 쌓은 제품으로, 차세대 HBM인 HBM4의 직전 세대다.

업계에서는 차후 HBM3E 12단 제품이 삼성전자의 HBM 경쟁력을 강화하는 열쇠가 될 것이라는 전망이 제기된다. HBM3E 8단 시장에서 열세에 몰렸던 삼성전자가 추후 12단 시장 선점을 통해 흐름을 뒤집을 수 있다는 분석이다. 삼성전자와 함께 HBM 시장 '양대 산맥'으로 꼽히는 SK하이닉스는 주요 고객사인 엔비디아에 HBM3E 8단 제품을 공급하며 명백한 선두 주자로 떠올랐다. 반면 삼성전자는 엔비디아와의 공식 납품 거래를 성사시키지 못하며 한동안 시장 경쟁에서 뒤처지는 모습을 보였다.

주목할 만한 부분은 최근 삼성전자가 공을 들이고 있는 HBM3E 12단 시장이 초기 단계에 머무르고 있다는 점이다. SK하이닉스가 선점한 8단 시장과 달리 아직까지 이렇다 할 '선두 주자'가 없다는 의미다. 익명을 요구한 한 업계 관계자는 "아직 엔비디아에 HBM3E 12단을 공급할 메모리 기업은 결정되지 않은 상태다. 삼성전자가 양산을 서두를 수밖에 없는 상황"이라며 "SK하이닉스와 삼성전자 중 먼저 엔비디아의 품질 테스트를 통과하고, HBM3E 12단 제품 공급을 선점하는 기업이 하반기 HBM 시장을 주도하게 될 것"이라고 진단했다.

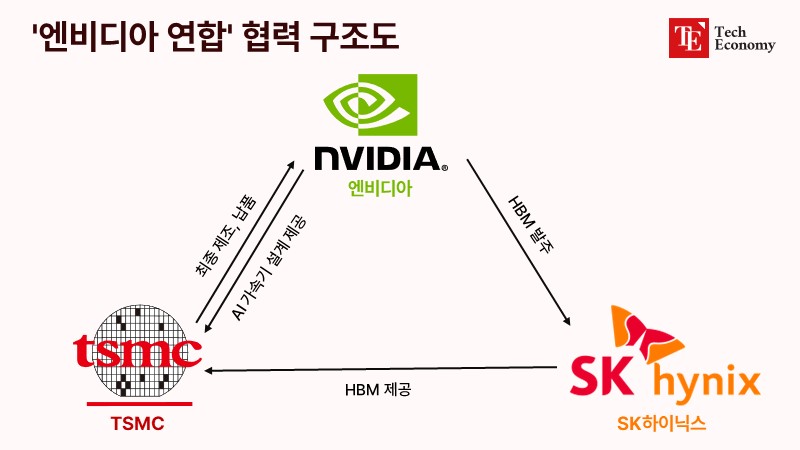

AI 가속기 생태계 재편 가능성

일각에서는 삼성전자가 HBM3E 12단 경쟁에서 승기를 거머쥘 경우 엔비디아와 TSMC, SK하이닉스가 주도하는 AI 가속기 시장 생태계에 지각변동이 발생할 수 있다는 분석도 흘러나온다. 현재 엔비디아 AI 가속기에 들어가는 GPU(그래픽처리장치)는 엔비디아가 설계를, 대만 TSMC가 생산을 담당하며, HBM은 SK하이닉스가 납품한다. HBM과 GPU의 패키징은 TSMC 몫이다. TSMC가 엔비디아의 GPU를 생산하고, SK하이닉스의 HBM을 받아 패키징한 뒤 재차 엔비디아에 납품하는 방식이다.

삼성전자가 엔비디아에 HBM 제품을 납품하기 위해서는 이들 기업이 선제적으로 만들어 둔 '틀'에 제품을 맞춰야 한다. 엔비디아의 요구 성능에 맞춰 SK하이닉스 못지않은 HBM을 생산할 수 있다는 걸 입증해야 하며, HBM을 받아 패키징 작업을 수행하는 TSMC와의 궁합도 맞출 필요가 있다. 1993년 이후 30년 넘게 세계 메모리 반도체(D램, 낸드플래시) 시장을 이끌어온 삼성전자가 경쟁사의 기준에 맞춰 고개를 숙여야 하는 상황이 연출된 셈이다.

이런 가운데 만약 삼성전자가 HBM3E 12단 제품을 엔비디아에 최초로 납품하는 데 성공한다면 상황은 뒤집히게 된다. SK하이닉스의 행보를 뒤따르는 데 급급했던 삼성전자가 HBM 경쟁에서 앞서며 시장의 '판'을 새롭게 짤 수 있게 된다는 의미다.

HBM4 경쟁에서도 '도전장'

삼성전자는 HBM3E 12단의 차세대 제품인 HBM4 개발에도 총력을 기울이고 있다. 15일 반도체 업계에 따르면 삼성전자는 HBM4의 로직 다이 제작에 4㎚ 파운드리 공정을 활용할 예정이다. 로직 다이는 HBM의 최하단에 배치되는 부품으로, 인간의 두뇌와 같은 핵심적인 역할을 수행한다. HBM3E까지는 메모리 반도체 기업이 로직 다이를 제조했지만, HBM4부터는 각각의 고객사가 요구하는 기능을 ‘맞춤형’으로 탑재할 필요가 있어 반드시 파운드리 공정을 거쳐야 한다.

HBM4 로직 다이 제작에 활용될 4㎚ 파운드리는 70%가 넘는 수율을 자랑하는 삼성전자의 ‘간판 공정’이다. 반도체 업계 관계자는 “4㎚ 공정은 7~8㎚에 비해 비용이 많이 들지만, 보다 섬세하게 회로를 그려 넣을 수 있어 칩 성능과 전력 사용량 측면에서 엄청난 강점이 있다”며 “현재 10㎚대 공정으로 HBM3E를 제작하는 삼성이 단번에 4㎚까지 적용 공정 수준을 끌어올린 것은 사실상 HBM 시장에 '도전장'을 던진 것이나 다름없다"고 평가했다.